IPAセキュリティ・キャンプ全国大会2022 Y4クラスの「RISC-V CPU自作ゼミ」で使用されている「RISC-VとChiselで学ぶ はじめてのCPU自作」の参考出力をここにまとめました。

- ソースコード:https://github.com/chadyuu/riscv-chisel-book)

- GOWIN EDA, openFPGALoaderの設定手順:https://github.com/ciniml/seccamp_2022_riscv_cpu/blob/main/slide/slide_0_pre.pdf

目次

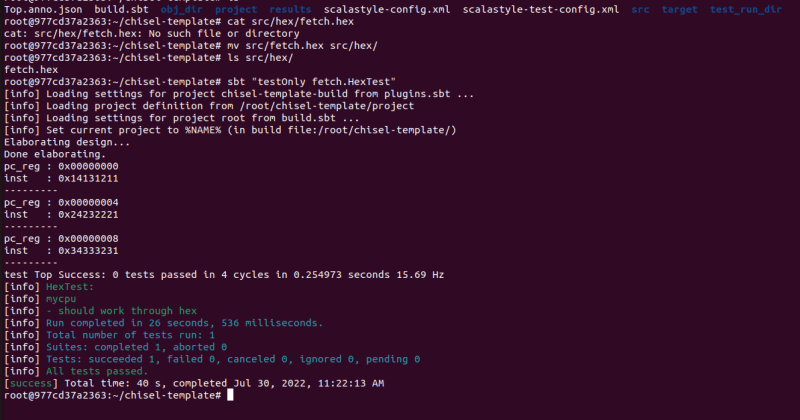

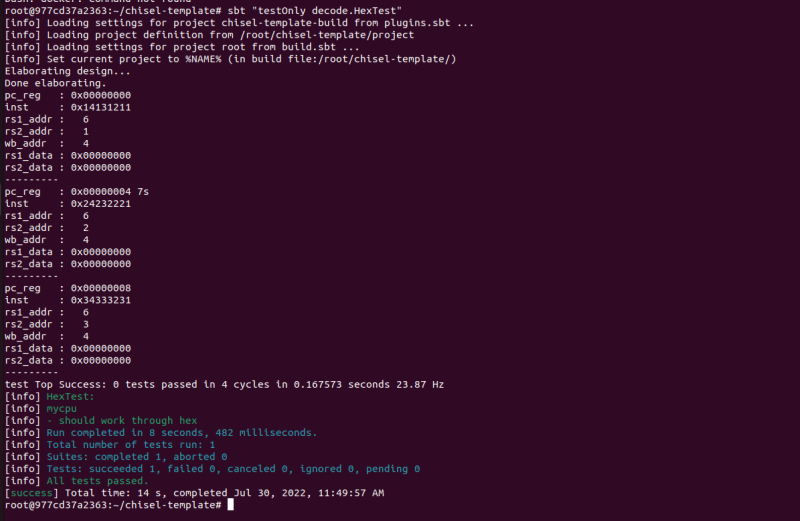

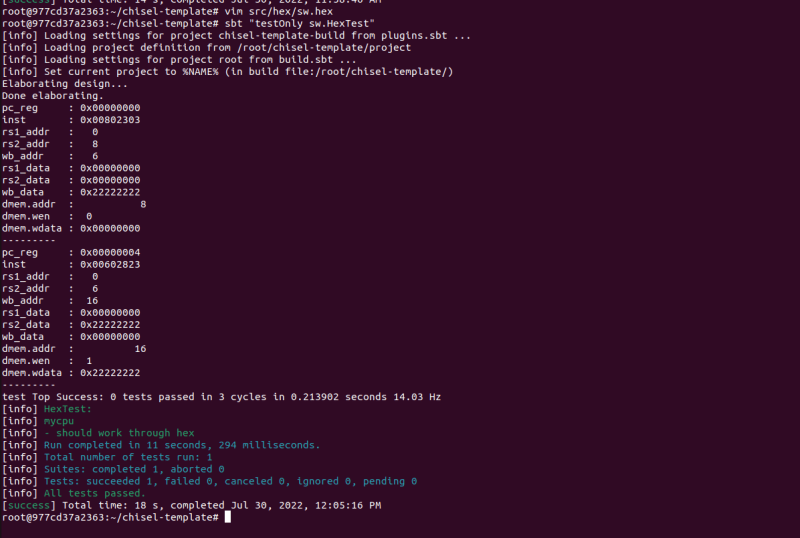

簡単なCPUの実装

使用環境:VirtualBox Ubuntu 22.04

ELFファイルをBINファイルへ変換, BINファイルのHex化 (p.148)

riscv-testsのテスト (p.154)

(この後にディレクトリを~/chisel-templateから~/src/chisel-templateに変えました)

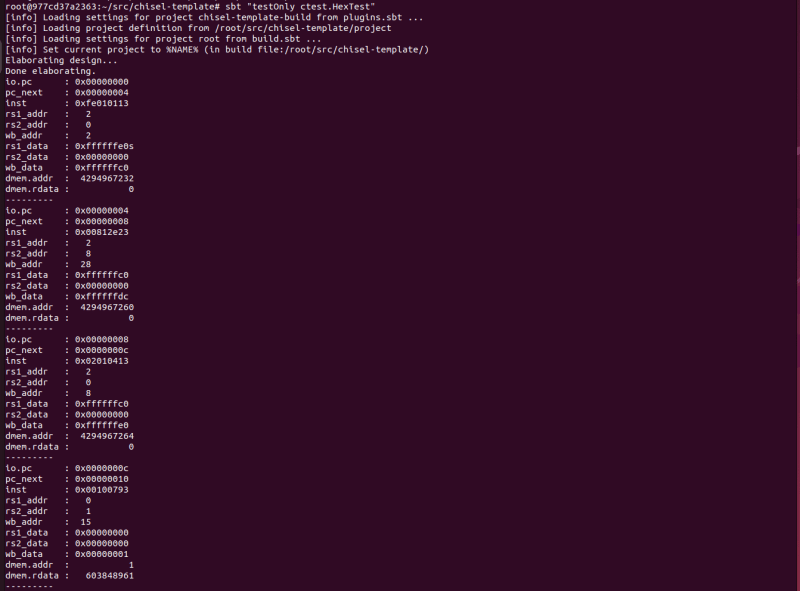

パイプラインの実装

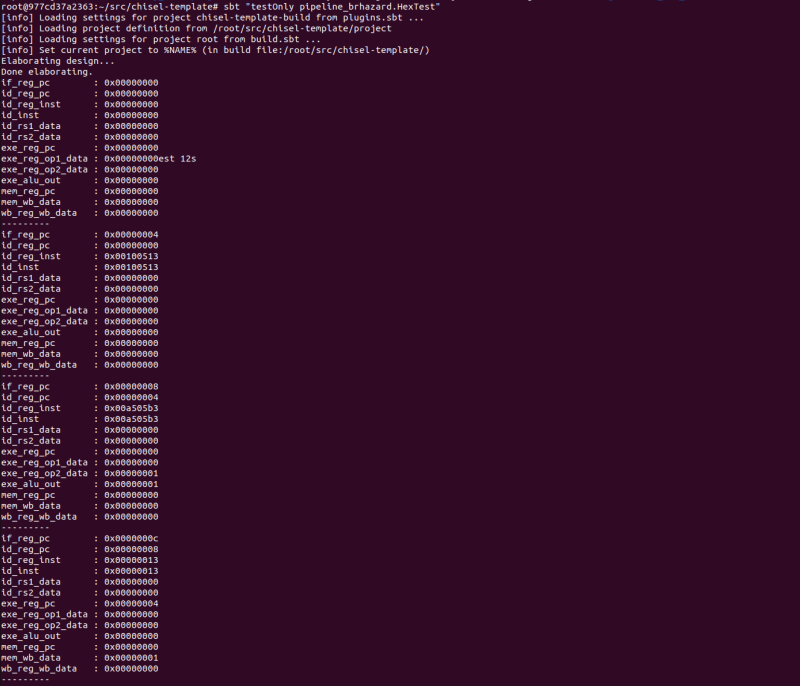

データハザード対応後CPUでのテスト (p.208)

GOWIN EDAでビットストリームを作成

使用環境:Windows 10

top.svのSystemVerilogコード:

module top(

input wire clock,

output logic [5:0] led

);

initial begin

led <= 0;

end

logic [24:0] counter = 0;

always_ff @(posedge clock) begin

if( counter < 25'd27_000_000 ) begin

counter++;

end

else begin

led <= ~led;

counter <= '0;

end

end

endmodule

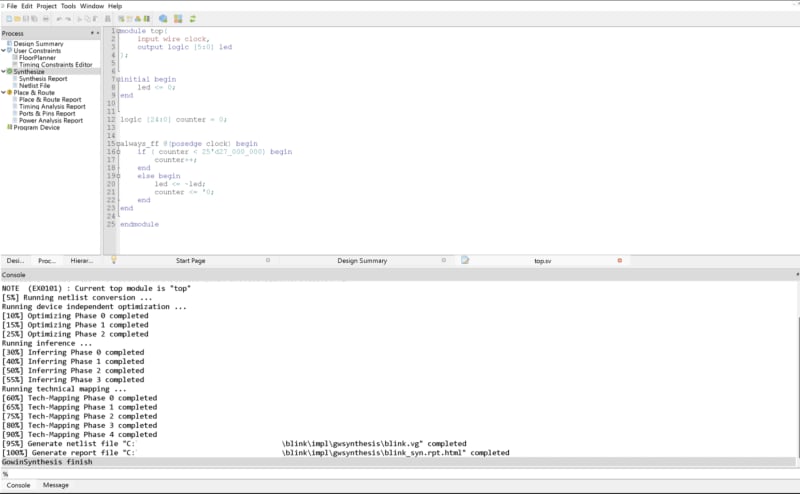

Synthesizeが成功した時の出力:

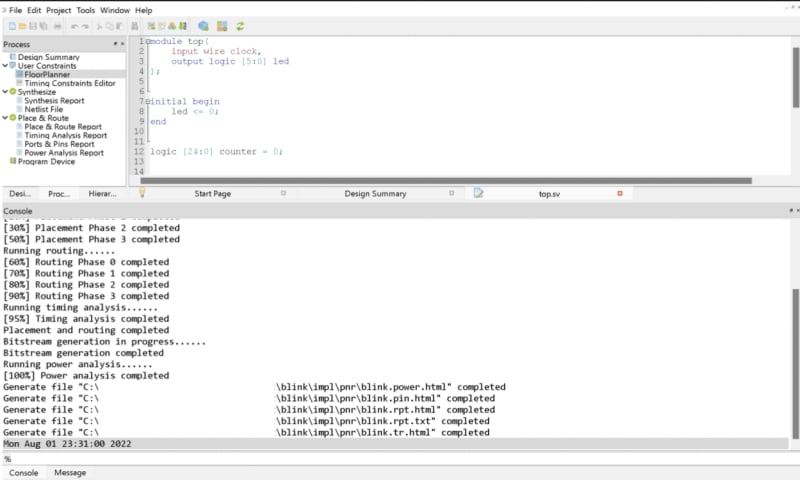

フロアプランのIO TypeはLVCMOS33を使用しました。

blink.fsがプロジェクトディレクトリに作成されました。

openFPGALoaderでTang Nanoに書き込む

openFPGALoaderのインストール:

Tang Nanoをパソコンに接続した際:

openFPGALoaderでビットストリームをTang Nanoに書き込んだ時の出力:

Top comments (0)